Appearance

差分信号:以 LVDS 为经典例子

很多人第一次接触差分信号时,会把它理解成“把一根线变成两根线”。

这个理解不算错,但远远不够。

差分真正改变的,不是导线数量,而是判决方式:接收端从“看某根线对地电压”,改成“看两根线之间的电压差”。

这篇文章只做一件事:把差分信号本身讲透。低压差分信号(Low Voltage Differential Signaling,LVDS)只在后文点到为止,作为经典例子引入。至于 LVDS 的参数细节和设计实践,会在后续专文展开。

1. 为什么要学差分信号

先从一个常见现象开始。

一条链路在低速下跑得很稳,速率一提上去,偶发误码就出现了,驱动端输出1010 1010,接收端接收0000 0000。协议没变,逻辑没变,代码也没变,结果却变差了。

这类问题通常不是“数字逻辑错了”,而是“电气判决环境变差了”。

单端信号(Single-Ended Signaling)在高速下常见三个压力:

- 高度的参考平面依赖与地弹效应

- 接收判决依赖“信号对地电压是否越过阈值”,地弹噪声(Ground Bounce)会直接影响判决裕量。

WARNING

不过需要注意,虽然差分信号通过互补参考缓解了地弹问题,但其极度惧怕物理不对称性,任何走线偏斜都会导致优势丧失并激发共模噪声。

- 不可控的回路面积与电磁干扰

- 单端信号的回流路径通常较难控制,导致等效回路面积偏大。随着信号边沿速率的不断提升(高频谐波剧增),过大的回路不仅会成倍放大对外的高频辐射,也使其更容易感应并吸收外界的电磁干扰。

- 阻抗敏感与串扰导致的眼图压缩

- 在复杂的物理链路中,单端信号对阻抗不连续极度敏感。寄生参数引起的信号反射,叠加相邻网络间的耦合串扰,会导致系统的等效判决窗口迅速缩小,进而引发眼图严重闭合。

高速链路设计的核心早已不再是单纯追求“速率(Speed)”,而是比拼极限条件下的“信号完整性(SI)”与“抗扰度”。这正是差分信号能够克服单端瓶颈,成为现代高速通信主流架构的底层逻辑。

[Image Placeholder: 单端与差分的判决方式对比]

- Purpose: 开篇建立问题意识,说明差分到底改变了什么。

- Should show: 单端对地判决路径、差分相减判决路径、共模干扰注入点。

差分不是“把线加倍”,而是“把判决逻辑升级”。

2.差分信号的本质:接收端看的是“相减结果”

差分对不是简单的两根线,而是一套“相减判决系统”。

- 差模电压(Differential Mode Voltage)

- 共模电压(Common Mode Voltage)

接收端主要关心差模电压,而不是某一根线相对地的绝对电压。这样做的好处是:

当外部噪声同时耦合到两根线上时,这部分同向扰动会主要进入共模分量,在相减后大幅抵消。

如果把接收端共模抑制比(Common-Mode Rejection Ratio,CMRR)记作 Acm,则共模噪声残留近似满足:

例如,当 Acm = 30 dB 时,100 mV 共模噪声只剩约 3.16 mV 的等效误差量级。

可以把它想成两个人抬担架:

- 路面整体抬高一点,二人同时上浮,担架相对姿态变化不大。

- 一边高一边低,才是真正影响担架平衡的“差分扰动”。

这就是差分链路抗干扰能力强的直觉来源。

❓ 那我问你:差分信号的两根走线靠得那么近,为什么它们之间不会产生破坏性的串扰(Crosstalk)?

面试官冷笑一声:“大家都知道布线要遵循 3W 原则来防串扰。既然你两根线贴得这么近,难道在差分信号这里,物理学定律就失效了吗?”

💡 点击查看满分回答

差分线内部的相互作用不属于非预期的“串扰”,而是设计上预期的“电磁耦合(Coupling)”。

- 磁场相消与能量约束:差分信号的P线和N线传输的是大小相等、方向相反的电流。根据右手螺旋定则,两者产生的磁场方向完全相反。当两根线紧密靠近时,它们在导线外部的磁场会相互抵消(不对外产生辐射和串扰);而在导线内部,磁场紧密交织,将电磁能量牢牢“束缚”在两根线之间,防止能量外泄。

- 预期的耦合构成“差分阻抗”:串扰的本质是非预期的、随机的能量耦合。而差分对中P与N之间的电磁感应是预期的、同步的。在设计时,已经将这种强烈的相互耦合计算在内。这种耦合直接构成了传输线的“差分阻抗”(如标准的 100Ω)。只要两根线的间距保持恒定,这种互相的吸引力就是稳定的,信号就能无反射地平稳传输。

- 紧密耦合实现“共模抑制(CMRR)”:差分走线靠得越紧,意味着外部干扰源到达P线和N线的空间距离越趋于绝对相等。距离相等使得外部干扰在两根线上感应出的噪声幅度相同、相位相同,这被称为“共模噪声”。

总结:差分线之间不是不可控的串扰,而是精密设计的耦合。它们通过紧密靠拢,对外实现了磁场抵消与共模免疫,对内实现了能量锁定与阻抗稳定。对差分信号而言,“距离产生美”是错的,“亲密无间”才是维持高速稳定的核心密码。

❓❓ 那我接着问你

如果差分线在布线时遇到过孔或障碍,被迫短暂分开(间距变大),会发生什么?

再补一层工程视角:如果两根线几何对称且耦合稳定,外泄场会部分互相抵消,这也是差分在电磁兼容(Electromagnetic Compatibility,EMC)上更有优势的原因之一。

[Image Placeholder: 差模与共模关系示意]

- Purpose: 把术语和物理图像对应起来,避免只背定义。

- Should show: Vp、Vn、Vdiff、Vcm 的关系,以及共模噪声叠加示意。

过渡:理解“为什么有效”之后,接下来要看“工程里怎么用不会翻车”。

3. 差分信号的优势与代价

差分信号不是“无脑更好”,而是“在特定目标下更合适”。

3.1 主要优势

- 抗共模干扰能力强。

- 辐射更容易控制。

- 适合更高边沿速率和更紧张的时序预算。

3.2 必须接受的代价

- 布线约束更严格。

- 阻抗和端接更敏感。

- 调试门槛更高,必须结合波形和误码统计。

3.3 一句话结论

差分不是“更高级”,而是“更工程化”。你用它换来的不是花哨,而是可控。

4. 工程实现里最容易忽略的关键点

这一节不绑定任何特定器件或协议,只讲通用方法。

4.1 阻抗连续性

链路中的过孔、连接器、焊盘突变都会造成阻抗台阶,进而带来反射。反射不一定马上导致通信失败,但会稳定地吞掉眼图余量。

4.2 对称性与等长

差分对两根线如果传播延时不一致,差模能量会被转换为共模分量。换句话说,你本来想用差分抵抗共模,结果自己制造了共模。

4.3 参考平面连续性

很多问题不是发生在“差分线本身”,而是发生在“回流路径被破坏”。一旦跨分割平面,链路稳定性和辐射表现通常会同时变差。

4.4 调试顺序

建议遵循这个顺序:

- 先看供电和参考时钟是否稳定。

- 再看链路波形和眼图余量。

- 最后看协议层统计与异常处理策略。

[Image Placeholder: 差分布线正确与错误对比]

- Purpose: 让读者看到“规则背后的物理代价”。

- Should show: 正确走线示例、跨分割平面错误示例、端接位置对比。

过渡:到这里,你已经掌握了差分的主干。下面只用一个段落引入 LVDS,作为经典例子点到为止。

5. 顺带提一嘴 LVDS:差分思想的经典落地

低压差分信号(Low Voltage Differential Signaling,LVDS)是差分家族里非常经典的实现。

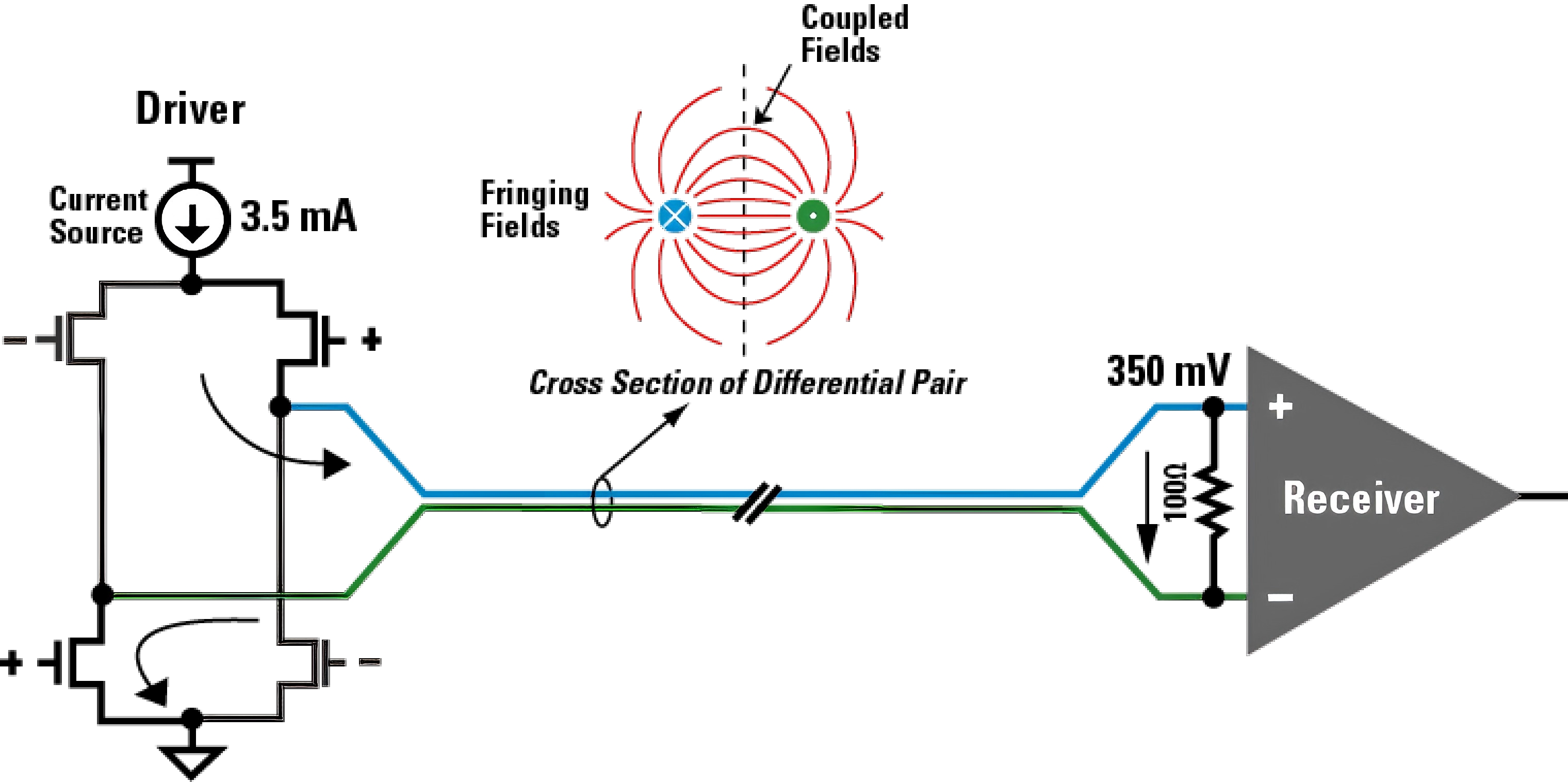

如上图所示为 LVDS 信号的 Driver 和 Receiver,你可以先记住它的三个典型标签:

1.低摆幅,常见差分摆幅约350mV。

2.恒流驱动,3.5mA配合终端电阻形成稳定电压摆动。

3.典型差分终端为 100 Ω。

它为什么经典?因为它把“差分的抗扰性”和“高速下的功耗压力”做了一个很实用的平衡。

很多资料会给出一个典型量级:

这也是“LVDS 经常作为差分入门例子”的原因。

这里不展开更多细节参数。后续会有单独的 LVDS 专题文章,专门讲规范边界、设计细节和调试方法。

6.顺带提一句 FPGA 对 LVDS 的支持

很多 FPGA 器件提供 LVDS I/O 标准和差分引脚资源,因此在实际项目里常看到“FPGA + LVDS”组合。

但这篇文章不讨论 FPGA 实现细节,只给三个方向提示:

1.先看器件手册是否支持目标电气标准。

2.再看 I/O Bank 与供电规则是否满足。

3.最后确认时序约束是否完整。

如果你只是刚开始学习差分,这一节知道“FPGA 常支持 LVDS”就足够了。

7.总结

差分信号的核心价值,不在于“线变多了”,而在于“判决方式变了”。

它把高速链路最难处理的一类问题,也就是共模干扰和判决裕量问题,变成了可设计、可验证、可优化的工程对象。

LVDS 是差分思想的经典实现,但不是本文重点。本文的目标是先让你建立底层认知。等你理解了差模、共模、对称性、阻抗和回流路径,再去看任何具体标准,都会更快更稳。